(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3992849号 (P3992849)

(45) 発行日 平成19年10月17日(2007.10.17)

(24) 登録日 平成19年8月3日(2007.8.3)

(51) Int.C1. F I **HO3M** 1/66 (2006.01)

HO3M

1/66

(2006.01)

HO3M

1/66

C

HO3M

1/52

(2006.01)

HO3M

1/66

A

HO3M

1/52

請求項の数 5 (全 17 頁)

(21) 出願番号 特願平10-218532

(22) 出願日 平成10年7月16日 (1998.7.16)

(65) 公開番号 特開2000-36748 (P2000-36748A)

(43) 公開日 平成12年2月2日 (2000.2.2) 審査請求日 平成17年6月27日 (2005.6.27) (73)特許権者 591220850

新潟精密株式会社

新潟県上越市西城町2丁目5番13号

||(74)代理人 100103171

弁理士 雨貝 正彦

(72) 発明者 小柳 裕喜生

新潟県上越市西城町2丁目5番13号 新

潟精密株式会社内

|(72)発明者 寅市 和男

埼玉県狭山市入間川1-14-2

審査官 柳下 勝幸

最終頁に続く

(54) 【発明の名称】デジタルーアナログ変換器

# (57)【特許請求の範囲】

### 【請求項1】

所定間隔で<u>連続的に</u>入力される複数のデジタルデータ<u>を、それぞれ</u>所定期間保持する複数のデータ保持部と、

前記複数のデータ保持部のそれぞれに保持されたデジタルデータに対応する所定の階段 関数を、<u>それぞれの</u>前記デジタルデータの<u>入力タイミング</u>に同期させて発生する複数の階 段関数発生部、

複数の前記階段関数発生部のそれぞれによって発生した前記階段関数の値を加算する加 算部と、

前記加算部による加算処理によって得られたデジタルデータに対応する階段状のアナログ電圧を生成する階段電圧波形発生部と、

前記階段電圧波形発生部によって生成されたアナログ電圧<u>を</u>複数回のアナログ積分を行う積分処理部と、<u>を備え、</u>

前記複数のデータ保持部は、連続的に入力される前記データを巡回的に保持し、

前記階段関数発生部は、M および N がそれぞれ 2 以上の整数、標本位置を t としたときに、  $t = \pm M$  でゼロに収束し、 t = 0 で 1 の値を、  $t = \pm 1$  …  $\pm M$  の時ゼロの値を有する N 次の区分多項式で構成されている標本化関数を、N 回微分することにより定義される階段関数を発生し、

<u>前記積分処理部は、前記階段状のアナログ電圧をN回積分す</u>ることを特徴とするデジタル・アナログ変換器。

# 【請求項2】

# 請求項1において、

前記階段関数は、正領域と負領域の面積が等しく設定されていることを特徴とするデジタル・アナログ変換器。

# 【請求項3】

### 請求項1または2において、

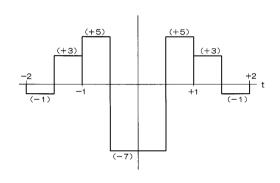

前記階段関数は、等間隔に配置された5つの前記デジタルデータに対応した所定範囲において、1、+3、+5、-7、-7、+5、+3、-1の重み付けがなされた同じ幅の8つの区分領域からなっていることを特徴とするデジタル・アナログ変換器。

### 【請求項4】

10

請求項3において、

前記階段関数は、前記重み付けのそれぞれを、ビットシフトによる - 2 、 + 2 、 + 4 、 - 8 、 - 8 、 + 4 、 + 2 、 - 2 倍の乗算処理を行った結果に対して前記デジタルデータ自身を加算することによって実現することを特徴とするデジタル - アナログ変換器。

### 【請求項5】

請求項1~4のいずれかにおいて、

前記アナログ積分が行われる回数は2回であり、複数の前記デジタルデータに対応した電圧をなめらかにつなぐ連続したアナログ信号を発生させることを特徴とするデジタル・アナログ変換器。

## 【発明の詳細な説明】

20

30

40

50

# [0001]

# 【発明の属する技術分野】

本発明は、離散的なデジタルデータを連続的なアナログ信号に変換するデジタル・アナログ変換器に関する。なお、本明細書においては、関数の値が局所的な領域で 0 以外の有限の値を有し、それ以外の領域で 0 となる場合を「有限台」と称して説明を行うものとする

# [0002]

# 【従来の技術】

最近のデジタルオーディオ装置、例えばCD(コンパクトディスク)プレーヤ等においては、離散的な音楽データ(デジタルデータ)から連続的なアナログの音声信号を得るためにオーバーサンプリング技術を適用したD/A(デジタル・アナログ)変換器が用いられている。このようなD/A変換器は、入力されるデジタルデータの間を補間して擬似的にサンプリング周波数を上げるために一般にはデジタルフィルタが用いられており、各補間値をサンプルホールド回路によって保持して階段状の信号波形を生成した後にこれをローパスフィルタに通すことによって滑らかなアナログの音声信号を出力している。

# [0003]

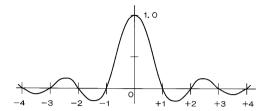

ところで、D/A変換器に含まれるデジタルフィルタによるデータ補間は、一般にはsinc関数と称される標本化関数を用いて行われる。図13は、sinc関数の説明図である。sinc関数は、ディラックのデルタ関数を逆フーリエ変換したときに現れるものであり、標本化周波数をfとしたときにsin(ft)/(ft)で定義される。このsinc関数は、t=0の標本点のみで1になり、他の全ての標本点では0となる。

### [0004]

従来は、この s in c 関数の波形データを F IR (finite impulse response ) フィルタのタップ計数に設定したデジタルフィルタを用いることにより、オーバーサンプリングを行っている。

# [0005]

### 【発明が解決しようとする課題】

ところで、デジタルフィルタによって離散的な音声データ間の補間演算を行うオーバーサンプリング技術を用いると、減衰特性がなだらかなローパスフィルタを用いることができるため、ローパスフィルタによる位相特性を直線位相特性に近づけるとともに標本化折返

30

40

50

し雑音を低減することが可能になる。このような効果は擬似的なサンプリング周波数を上げれば上げるほど顕著になるが、サンプリング周波数を上げるとそれだけデジタルフィルタやサンプルホールド回路の処理速度も高速化されるため、高速化に適した高価な部品を使用する必要があり、部品コストの上昇を招く。また、画像データのように本来のサンプリング周波数自体が高い場合(例えば数MHz)には、これをオーバーサンプリングするには数十MHzから数百MHzで動作可能な部品を用いてデジタルフィルタやサンプルホールド回路を構成する必要があり、その実現が容易ではなかった。

# [0006]

また、オーバーサンプリング技術を用いた場合であっても、最終的には階段状の信号波形をローパスフィルタに通して滑らかなアナログ信号を生成しているため、ローパスフィルタを用いている限り厳密な意味での直線位相特性を持たせることができなかった。また、上述したsinc関数は、± で0に収束する関数であるため、正確な補間値を求めようとすると、全てのデジタルデータの値を考慮する必要があるが、実際は回路規模等の都合から、考慮するデジタルデータの範囲を限定してデジタルフィルタのタップ係数の数が設定されており、得られる補間値には打ち切り誤差が含まれていた。

#### [0007]

このように、オーバーサンプリング技術を適用した従来の D / A 変換器は、擬似的にサンプリング周波数を上げるために高速な部品が必要であって、コスト高を招いたり、あるいは実現が容易ではかった。また、ローパスフィルタを通すため位相特性の劣化があり、しかも s in c 関数を適用したデジタルフィルタを用いているため打ち切り誤差が含まれ、これらに対応した出力波形の歪みが生じていた。

#### [0.008]

本発明は、このような点に鑑みて創作されたものであり、その目的は、部品の動作速度を上げることなく歪みの少ない出力波形を得ることができるデジタル - アナログ変換器を提供することにある。

### [0009]

# 【課題を解決するための手段】

上述した課題を解決するために、本発明のデジタル・アナログ変換器は、入力されたデジタルデータのそれぞれに対応する値を有する所定の階段関数を発生させてこれらを加算し、階段状のアナログ電圧に変換した後に複数回のアナログ積分を行うことによって、順に入力される各デジタルデータに対応する電圧をなめらかにつなぐ連続したアナログ信号を発生する。このように、順に入力される複数のデジタルデータに対応する所定の階段関数を複数のデジタルデータのそれぞれについて発生させて各階段関数の値を加算し、その後この加算結果をアナログ電圧に変換して積分することにより連続的に変化するアナログ信号が得られるため、最終的なアナログ信号を得るためにローパスフィルタを用いる必要がなく、扱う信号の周波数によって位相特性が異なるために群遅延特性が悪化するといったことがなく、歪みの少ない出力波形を得ることができる。また、オーバーサンプリングを行っていた従来の手法に比べると、部品の動作速度を上げる必要がないため、高価な部品を使用する必要がなく、部品コストの低減が可能になる。

### [0010]

特に、上述した階段関数は、区分多項式によって構成された所定の標本化関数について、各区分多項式を複数回微分することにより得られる波形を用いることが好ましい。すなわち、反対にこの階段関数を複数回積分することにより、所定の標本化関数に対応した波形を得ることができるため、標本化関数による畳み込み演算を、階段関数を合成することによって等価的に実現することが可能になり、処理内容を単純化することができるため、デジタルデータをアナログ信号に変換するために必要な処理量の低減が可能になる。

# [0011]

また、上述した標本化関数は、全域が1回だけ微分可能であって有限台の値を有することが好ましい。自然界に存在する各種の信号は、滑らかに変化しているため微分可能性が必要であると考えられるが、その微分可能回数は必ずしも無限回である必要はなく、むしろ

1回だけ微分可能であれば充分に自然現象を近似できると考えられる。このように、有限回微分可能であって有限台な標本化関数を用いることにより数々の利点があるが、従来はこのような条件を満たす標本化関数が存在しないと考えられていた。ところが、本発明者の研究によって、上述した条件を満たす関数が見いだされた。

### [0012]

## [0013]

このように、全域で1回だけ微分可能な標本化関数を用いることにより、複数の階段関数を加算した後に積分処理する回数を減らすことができ、処理量を低減することが可能になる。また、有限台の値を有する標本化関数を用いることにより、この有限台の区間に対応したデジタルデータのみを処理の対象とすればよいため、さらに処理量を低減することができ、しかも有限個のデジタルデータを対象に処理を行った場合の打ち切り誤差の発生を防止することができる。

# [0014]

### 【発明の実施の形態】

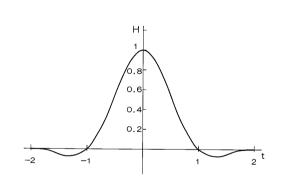

以下、本発明を適用した一実施形態の D / A 変換器について、図面を参照しながら詳細に説明する。図 1 は、本実施形態の D / A 変換器における補間演算に用いられる標本化関数の説明図である。図 1 に示す標本化関数 H (t) は、微分可能性に着目した有限台の関数であり、例えば全域において 1 回だけ微分可能であって、横軸に沿った標本位置 t が - 2 から + 2 の間にあるときに 0 以外の有限な値を有する有限台の関数である。また、 H (t) は標本化関数であるため、 t=0 の標本位置のみで 1 になり、  $t=\pm1$  ,  $\pm2$  の標本位置において 0 になるという特徴を有する。

# [0015]

上述した各種の条件(標本化関数、 1 回だけ微分可能、有限台)を満たす関数 H ( t ) が存在することが本発明者の研究により確かめられている。具体的には、このような標本化関数 H ( t ) は、 3 階 B スプライン関数を F ( t ) としたときに、

H(t) = -F(t+1/2)/4+F(t)-F(t-1/2)/4...(1)

で定義することができる。ここで、 3 階 B スプライン関数 F ( t ) は、

$(4 t^{2} + 1 2 t + 9) / 4$  ; -3 / 2 t < -1 / 2  $-2 t^{2} + 3 / 2$  ; -1 / 2 t < 1 / 2

$(4t^2 - 12t + 9)/4$  ; 1/2 t < 3/2 ... (2)

### で表される。

# [0016]

上述した標本化関数 H ( t ) は、二次の区分多項式であり、 3 階 B スプライン関数 F ( t ) を用いているため、全域で 1 回だけの微分可能性が保証される有限台の関数となっている。また、  $t=\pm1$  ,  $\pm2$  の標本位置において 0 となる。

# [0017]

40

20

上述した(2)式を(1)式に代入して、標本化関数H(t)を区分多項式の形で求める と、

$(-t^2 - 4t - 4)/4$ ; - 2 t < - 3 / 2  $(3t^2 + 8t + 5) / 4$ ; - 3 / 2 t < - 1  $(5t^2 + 12t + 7)/4$ ; - 1 t < - 1 / 2  $(-7t^2+4)/4$ ; - 1 / 2 t < 1 / 2  $(5t^2 - 12t + 7)/4$ ; 1 / 2 t < 1  $(3t^2 - 8t + 5) / 4$ ; 1 t < 3 / 2  $(-t^2 + 4t - 4)/4$ ; 3 / 2 t 2 ... (3)

と表すことができる。

## [0018]

このように、上述した関数H(t)は、標本化関数であって、全域において1回だけ微分 可能であり、しかも標本位置t=±2において0に収束する有限台の関数である。したが って、この標本化関数H(t)を用いて各標本値に基づく重ね合わせを行うことにより、 標本値間の値を1回だけ微分可能な関数を用いて補間することができる。

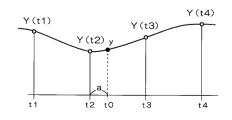

図2は、標本値とその間の補間値との関係を示す図である。一般に、与えられた各標本値 のそれぞれについて補間位置における標本化関数の値を求め、これを用いて畳み込み演算 を行うことにより、各標本値の間の中間位置に対応する補間値 y を求めることができる。

[0020]

従来から用いられているsinc関数はt=t の標本位置で0に収束する関数であるた め、補間値 V を正確に求めようとすると、 t = ± までの各標本値に対応して補間位置で のsinc関数の値を計算し、これを用いて畳み込み演算を行う必要があった。ところが 本実施形態で用いる標本化関数H(t)は、t=±2の標本位置で0に収束するため、 補間位置を挟んで前後2個ずつの標本値を考慮すればよく、演算量を大幅に削減すること ができる。しかも、それ以外の標本値については、本来考慮すべきであるが演算量や精度 等を考慮して無視しているというわけではなく、理論的に考慮する必要がないため、打ち 切り誤差は発生しない。

# [0021]

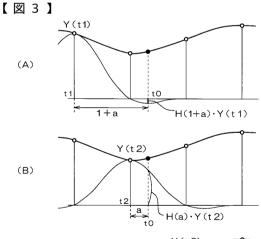

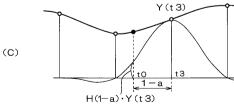

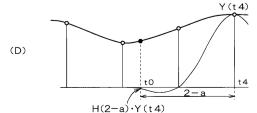

図3は、図1に示す標本化関数を用いたデータ補間の説明図である。例えば、図3(A) に示す標本位置t1における標本値Y(t1)について具体的に説明する。補間位置t0 と標本位置t1との距離は、隣接する2つの標本位置間の距離を正規化して1とすると、 1 + a となる。したがって、標本位置 t 1 に標本化関数 H ( t ) の中心位置を合わせたと きの補間位置t0における標本化関数の値はH(1+a)となる。実際には、標本値Y( t1)に一致するように標本化関数H(t)の中心位置のピーク高さを合わせるため、上 述したH(1+a)をY(t1)倍した値H(1+a)・Y(t1)が求めたい値となる

[0022]

同様にして、図3(B)~(D)に示すように、他の3つの標本値に対応して、補間位置 t 0 における各演算結果 H ( a ) ・ Y ( t 2 ) 、 H ( 1 - a ) ・ Y ( t 3 ) 、 H ( 2 - a )・Y(t4)が得られる。このようにして得られた4つの演算結果H(1+a)・Y( t1)、H(a)·Y(t2)、H(1-a)·Y(t3)、H(2-a)·Y(t4) を加算して畳み込み演算を行うことにより、補間位置t 0 における補間値 y が求められる

### [0023]

ところで、上述したように、原理的には各標本値に対応させて標本化関数H(t)の値を 計算して畳み込み演算を行うことにより各標本値の間の中間位置に対応する補間値を求め ることができるが、図1に示した標本化関数は全域で1回だけ微分可能な二次の区分多項 式であり、この特徴を利用して、等価的な他の処理手順によって補間値を求めることがで きる。

20

10

30

### [0024]

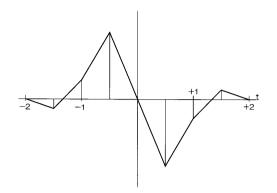

図4は、図1に示した標本化関数を1回微分した波形を示す図である。図1に示した標本化関数H(t)は、全域で1回微分可能な二次の区分多項式であるため、これを1回微分することにより、図4に示すような連続的な折れ線状の波形からなる折れ線関数を得ることができる。

### [0025]

また、図5は図4に示した折れ線関数をさらに微分した波形を示す図である。但し、折れ線波形には複数の角点が含まれており、全域で微分することはできないため、隣接する2つの角点に挟まれた直線部分について微分を行うものとする。図4に示す折れ線波形を微分することにより、図5に示すような階段状の波形からなる階段関数を得ることができる

### [0026]

このように、本実施形態の D / A 変換器における補間演算に用いられる標本化関数は、全域を 1 回微分して折れ線関数が得られ、この折れ線関数の各直線部分をさらに微分することにより階段関数が得られる。したがって、反対に図 5 に示した階段関数を発生させ、これを 2 回積分することにより、図 1 に示した標本化関数 H (t)を得ることができる。

### [0027]

なお、図 5 に示した階段関数は正領域と負領域とが等しい面積を有しており、これらを合計した値が 0 となる特徴を有している。換言すれば、このような特徴を有する階段関数を複数回積分することにより、図 1 に示したような全域における微分可能性が保証された有限台の標本化関数を得ることができる。

#### [0028]

ところで、図3に示した畳み込み演算による補間値の算出では、標本化関数 H ( t ) の値に各標本値を乗算したが、図5に示した階段関数を2回積分して標本化関数 H ( t ) を求める場合には、この積分処理によって得られた標本化関数の値に各標本値を乗算する場合の他に、等価的には、積分処理前の階段関数を発生させる際に、各標本値が乗算された階段関数を発生させ、この階段関数を用いて畳み込み演算を行った結果に対して2回の積分処理を行って補間値を求めることができる。本実施形態のD / A 変換器は、このようにして補間値を求めており、次にその詳細を説明する。

### [0029]

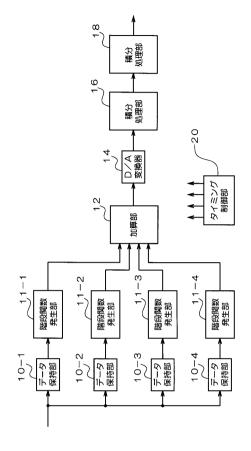

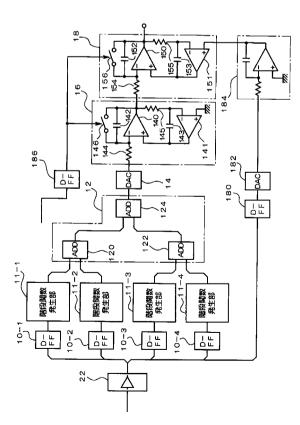

図 6 は、本実施形態の D / A 変換器の構成を示す図である。同図に示す D / A 変換器は、4 つのデータ保持部 1 0 - 1、1 0 - 2、1 0 - 3、1 0 - 4、4 つの階段関数発生部 1 1 - 1、1 1 - 2、1 1 - 3、1 1 - 4、加算部 1 2、 D / A 変換器 1 4、2 つの積分処理部 1 6、1 8、タイミング制御部 2 0を含んで構成されている。

# [0030]

各データ保持部10-1~10-4は、所定の時間間隔で順次入力される離散的なデジタルデータを巡回的に選択して取り込み、次の取り込みタイミングが到来するまでその値を保持する。例えば、最初に入力されるデジタルデータがデータ保持部10-1に保持され、2番目に入力されるデジタルデータがデータ保持部10-2に保持される。また、3番目、4番目に入力される各デジタルデータがデータ保持部10-3、10-4に保持される。各データ保持部10-1~10-4におけるデータの保持動作が一巡すると、次に入力される5番目のデジタルデータは、一番早くデータを保持したデータ保持部10-1に取り込まれて保持される。このようにして、順に入力される各デジタルデータがデータ保持部10-1等によって巡回的に保持される。

### [0031]

各階段関数発生部 1 1 - 1 ~ 1 1 - 4 は、対応するデータ保持部 1 0 - 1 ~ 1 0 - 4 によるデジタルデータの保持タイミングに同期して、それぞれの保持データの値に比例した振幅(波高値)を有する階段関数を発生する。階段関数そのものは図 5 に示した形状を有しており、この階段関数の値が、データ保持部 1 0 - 1 ~ 1 0 - 4 のそれぞれに保持されたデジタルデータの値に比例している。図 5 に示した階段関数の具体的な値は、上述した(

0

20

30

40

3)式の各区分多項式を2回微分することにより得ることができ、以下のようになる。

## [0032]

- 1 ; - 2 t < - 3 / 2 3 ; - 3 / 2 t < - 1 5 ; - 1 t < - 1 / 2 - 7 ; - 1 / 2 0 - 7 ; 0 t < 1 / 2 5 ; 1 / 2 t < 1 3 ; 1 t < 3 / 2

: 3 / 2 t

10

20

加算部12は、4つの階段関数発生部11-1-1-4から出力されるそれぞれの階段関数の値をデジタル的に加算する。D/A変換器14は、加算部12から入力される階段状のデジタルデータに対応するアナログ電圧を発生する。このD/A変換器10では、入力されるデジタルデータの値に比例した一定のアナログ電圧を発生するため、入力されるデジタルデータに対応して階段状に電圧レベルが変化する出力電圧が得られる。

#### [0033]

縦続接続された2つの積分処理部16、18は、D/A変換器14の出力端に現れる階段状に変化する出力電圧に対して2回の積分処理を行う。前段の積分処理部16からは直線状(一次関数的)に変化する出力電圧が得られ、後段の積分処理部18からは二次関数的に変化する出力電圧が得られる。このようにして、複数のデジタルデータが一定間隔で入力されると、後段の積分処理部18からは、各デジタルデータに対応する電圧の間を1回だけ微分可能な滑らかな曲線で結んだ連続的なアナログ信号が得られる。

[0034]

ところで、上述した階段関数発生部11-1から出力される階段関数の値は、データ保持部10-1に保持されたデジタルデータの値に比例しているため、この階段関数の値に対応する電圧値に対して2つの積分処理部16、18によって積分処理を2回繰り返すことにより、後段の積分処理部18からは、図1に示した階段関数と入力されるデジタルデータとを乗算した結果に対応する電圧波形の信号が出力される。また、加算部12によって、各階段関数発生部11-1~11-4から出力される階段関数の値を加算するということは、後段の積分処理部18から出力される信号に着目すると、図1に示した階段関数を用いて畳み込み演算を行うことに他ならない。

30

40

50

# [0035]

したがって、本実施形態のD/A変換器にデジタルデータが一定の時間間隔で入力される場合を考えると、この入力間隔に対応させて各階段関数発生部11-1-4による階段関数波形の発生開始タイミングをずらし、それぞれにおいて発生した階段関数の加算を行い、その結果をアナログ電圧に変換した後に2回の積分処理を行うことにより、一定間隔で入力されるデジタルデータに対応した電圧間を滑らかに結ぶアナログ信号が得られる。

# [0036]

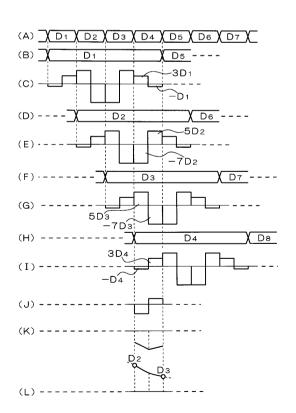

図7は、本実施形態のD/A変換器の動作タイミングを示す図である。図7(A)に示すように一定の時間間隔でデジタルデータ $D_1$ 、 $D_2$ 、 $D_3$ 、…が入力されると、各データ保持部10-1~10-4は、これらのデジタルデータ $D_1$ 、 $D_2$ 、 $D_3$ 、…を巡回的に保持する。具体的には、データ保持部10-1は、1番目に入力されるデジタルデータ $D_1$ を取り込んで、入力されるデジタルデータが一巡するまで(5番目のデジタルデータ $D_2$ が入力されるまで)保持する(図7(B))。また、この1番目のデジタルデータ $D_3$ の保持タイミングに合わせて、階段関数発生部11-1は、このデジタルデータ $D_4$ に比例した値を有する階段関数を発生する(図7(C))。

### [0037]

同様に、データ保持部 1 0 - 2 は、 2 番目に入力されるデジタルデータ  $D_2$  を取り込んで、入力されるデジタルデータが一巡するまで( 6 番目のデジタルデータ  $D_6$  が入力される

まで)保持する(図 7 ( D ))。また、この 2 番目のデジタルデータ D<sub>2</sub> の保持タイミングに合わせて、階段関数発生部 1 1 - 2 は、このデジタルデータ D<sub>2</sub> に比例した値を有する階段関数を発生する(図 7 ( E ))。

### [0038]

データ保持部  $1\ 0\ -\ 3$  は、 3 番目に入力される入力データ  $D_3$  を取り込んで、入力されるデジタルデータが一巡するまで(7 番目のデジタルデータ  $D_7$  が入力されるまで)保持する(図 7 ( F ) )。また、この 3 番目のデジタルデータ  $D_3$  の保持タイミングに合わせて、階段関数発生部  $1\ 1\ -\ 3$  は、このデジタルデータ  $D_3$  に比例した値を有する階段関数を発生する(図 7 ( G ) )。

# [0039]

データ保持部 1 0 - 4 は、4 番目に入力されるデジタルデータ  $D_4$  を取り込んで、入力されるデジタルデータが一巡するまで(8 番目のデジタルデータ  $D_8$  が入力されるまで)保持する(図 7 ( H ) )。また、この 4 番目のデジタルデータ  $D_4$  の保持タイミングに合わせて、階段関数発生部 1 1 - 4 は、このデジタルデータ  $D_4$  に比例した値を有する階段関数を発生する(図 7 ( I ) )。

### [0040]

加算部12は、このようにして4つの階段関数発生部11-1~11-4のそれぞれから出力される各階段関数の値を加算する。ところで、図5に示したように、各階段関数発生部11-1~11-4によって発生する階段関数は、図1に示した標本化関数の有限台の範囲である標本位置 t = - 2 ~ + 2 の領域を0.5 毎に分割した8 つの区分領域を有する有限台の関数である。例えば、標本位置 t = - 2 から + 2 に向かって順に第1区分領域、第2区分領域、…第8区分領域とする。

# [0041]

まず加算部12は、階段関数発生部11-1から出力される第7区分領域に対応する値(3 D<sub>1</sub> )と、階段関数発生部11-2から出力される第5区分領域に対応する値(-7D2 )と、階段関数発生部11-3から出力される第3区分領域に対応する値(5D3 )と、階段関数発生部11-4から出力される第1区分領域に対応する値(-D4 )とを加算して、加算結果(3D1 -7D2 +5D3 -D4 )を出力する。

# [0042]

次に、加算部12は、階段関数発生部11-1から出力される第8区分領域に対応する値(-D<sub>1</sub>)と、階段関数発生部11-2から出力される第6区分領域に対応する値(5 D<sub>2</sub>)と、階段関数発生部11-3から出力される第4区分領域に対応する値(-7 D<sub>3</sub>)と、階段関数発生部11-4から出力される第2区分領域に対応する値(3 D<sub>4</sub>)とを加算して、加算結果(-D<sub>1</sub>+5 D<sub>2</sub>-7 D<sub>3</sub>+3 D<sub>4</sub>)を出力する。

# [0043]

このようにして加算部12から順に階段状の加算結果が出力されると、D/A変換器14は、この加算結果(デジタルデータ)に基づいてアナログ電圧を発生する。このD/A変換器14では、入力されるデジタルデータの値に比例した一定のアナログ電圧が発生されるため、入力されるデジタルデータに対応して階段状に電圧レベルが変化する出力波形が得られる(図7(J))。

# [0044]

D/A 変換部 1.4 から階段状の電圧レベルを有する波形が出力されると、前段の積分処理部 1.6 は、この波形を積分して折れ線状の波形を出力し(図 7.0 ( K.0 ))、後段の積分処理部 1.8 は、この折れ線状の波形をさらに積分して、デジタルデータ  $D_2$  と  $D_3$  のそれぞれに対応した電圧値の間を 1 回だけ微分可能な滑らかな曲線で結ぶ出力電圧を発生する(図 7.0 ( L.0 ))。

### [0045]

このように、本実施形態の D / A 変換器は、入力されるデジタルデータを保持するタイミングに合わせて階段関数を発生させ、この階段関数を 4 つのデジタルデータについて加算した後にこの加算結果に対応したアナログ電圧を発生させ、さらにその後に 2 回の積分処

10

20

30

40

30

40

50

理を行うことにより、各デジタルデータに対応した電圧を滑らかにつなぐ連続したアナログ信号を発生することができる。

# [0046]

特に、入力される各デジタルデータに対応させて、それぞれが異なる開始タイミングで4つの階段関数を発生させ、この加算結果に対応するアナログ電圧を発生させた後に2回の積分処理を行うことにより、連続的なアナログ信号が得られるため、従来のようにサンプルホールド回路やローパスフィルタが不要であって直線位相特性が悪化することもなく、良好な群遅延特性を実現することができる。また、標本位置 t が ± 2 において 0 に収束する有限台の標本化関数 H (t)を用いているため、デジタルデータ間の補間処理を行うために前後 4 つのデジタルデータのみを用いればよく、補間演算を行うために必要な処理量を少なくすることができる。さらに、従来のようにオーバーサンプリング処理を行っていないため、入力されるデジタルデータの時間間隔に応じて決まる所定の動作速度を確保するだけでよく、特に高速な信号処理を行う必要もないため、高価な部品を用いる必要もない。

### [0047]

図 8 は、図 6 に示した D / A 変換器の詳細構成を示す図である。図 8 に示すように、各データ保持部 1 0 - 1 ~ 1 0 - 4 は D 型 フロップフロップ ( D - F F ) によって構成されており、バッファ 2 2 を介して入力されるデータに対して、取り込みタイミングを入力データの 1 周期分ずつ順番にずらしていくことにより、入力データ D  $_1$  、 D  $_2$  、 D  $_3$  、 …を巡回的に保持する。例えば、 8 ビットのデジタルデータが入力されるものとすると、各データ保持部 1 0 - 1 ~ 1 0 - 4 に保持された 8 ビットのデータは、それぞれに対応する階段関数発生部 1 1 - 1 ~ 1 1 - 4 に入力される。

# [0048]

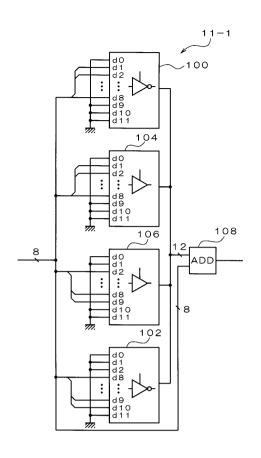

図9は、階段関数発生部11-1~11-4の詳細な構成を示す図である。なお、4つの階段関数発生部11-1~11-4は同じ構成を有しており、以下では、代表して階段関数発生部11-1の詳細について説明する。

### [0049]

図9に示すように、階段関数発生部11-1は、反転出力を有する2つのトライステートバッファ100、102と、非反転出力を有する2つのトライステートバッファ104、106と、この階段関数発生部11-1に入力されるデータとトライステートバッファ100~106のいずれかを介して出力されるデータとを加算する加算器(ADD)108とを含んで構成されている。

### [0050]

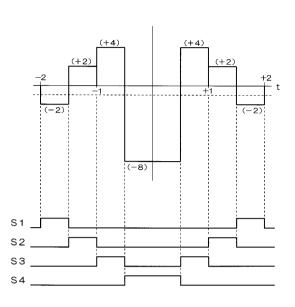

ところで、図 5 に示した階段関数は、横軸を上方向に + 1シフトすると図 1 0 に示す階段関数に変形される。この変形後の階段関数のそれぞれの値は、2 のべき乗の値になっているため、各値を乗数として入力データに対する乗算を行う場合には、単純なビットシフト操作によって乗算を実行することができる。その後、上方向に + 1シフトした横軸を元に戻す処理(乗算結果に入力データを加算する処理)を行って、各階段関数発生部の出力値とすればよい。

## [0051]

具体的には、トライステートバッファ100は、入力データに対して1ビット分シフトするとともに、そのシフトされたデータの各ビットを反転して出力すると同時に、加算器108のキャリー入力に1を加えることによって、(-2)倍の乗算が行われる。図10の「S1」で示すタイミングで、トライステートバッファ100から乗算結果に対応するデータを出力することにより、階段関数の第1および第8の区分領域に対応するデータが得られる。

### [0052]

同様に、トライステートバッファ102は、入力データを1ビット分シフトすることにより、2倍の乗算を行う。図10の「S2」で示すタイミングで、トライステートバッファ 102から乗算結果に対応するデータを出力することにより、階段関数の第2および第7

20

30

40

50

の区分領域に対応するデータが得られる。

### [0053]

トライステートバッファ 1 0 4 は、入力データを 2 ビット分シフトすることにより、 4 倍の乗算を行う。図 1 0 の「S3」で示すタイミングで、トライステートバッファ 1 0 4 から乗算結果に対応するデータを出力することにより、階段関数の第 3 および第 6 の区分領域に対応するデータが得られる。

#### [0054]

トライステートバッファ106は、入力データを3ビットシフトするとともに各ビットを反転し、加算器108のキャリー入力に1を加えることにより、(-8)倍の乗算を行う。図10の「S4」で示すタイミングで、トライステートバッファ100から乗算結果に対応するデータを出力することにより、階段関数の第4および第5の区分領域に対応するデータが得られる。

### [0055]

加算器 1 0 8 は、トライステートバッファ 1 0 0 ~ 1 0 6 のいずれかから選択的に出力される正あるいは負のデータと、階段関数発生部 1 1 - 1 に入力されるデータとを加算する。そして、加算器 1 0 8 によって得られるデータが階段関数 1 1 - 1 から出力される。

### [0056]

なお、加算器 1 0 8 では、ビットシフトされた結果を反転したトライステートバッファ 1 0 0、1 0 2 の出力データが入力されるか、あるいはビットシフトのみがなされたトライステートバッファ 1 0 4、1 0 6 の出力データが入力されるかによって、処理手順の詳細が異なる。すなわち、ビットシフトがされていないデータを用いて加算を行う場合には、単純に 2 つのデータの加算処理が行われる。また、ビット反転が行われたデータを用いて加算を行う場合には、2 つのデータを加算した後に最下位ビット b 0 に '1'を加算する。加算器 1 0 8 に入力されたデータがいずれの種類に属するかは、最上位ビットが'1'であるか否かを調べればよい。

### [0057]

図 8 に示す加算器 1 2 は、 2 つの入力端子を有する 3 つの加算器(A D D ) 1 2 0 、 1 2 2 、 1 2 4 によって構成されている。これら 3 つの加算器 1 2 0 、 1 2 2 、 1 2 4 によって、 4 つの階段関数発生部 1 1 - 1 ~ 1 1 - 4 から出力されるそれぞれのデータが加算される。この加算結果が D / A 変換器 (DAC) 1 4 に入力されて階段状の電圧波形に変換され、縦続接続された 2 つの積分処理部 1 6 、 1 8 のうちの前段の積分処理部 1 6 に印加される。

### [0058]

また、図8に示すように、前段の積分処理部16は、2つの演算増幅器140、141、2つのキャパシタ142、143、2つの抵抗144、145およびスイッチ146を含んで構成されている。一方の演算増幅器140とキャパシタ142および抵抗144によって積分回路が構成されており、抵抗144を介して演算増幅器140の反転入力端子に印加される D / A 変換器14の出力電圧に対して所定の積分動作が行われる。また、後段の積分処理部18は、2つの演算増幅器150、151、2つのキャパシタ152、153、2つの抵抗154、155およびスイッチ156を含んで構成されている。一方の演算増幅器150とキャパシタ152および抵抗154によって積分回路が構成されており、抵抗154を介して演算増幅器150の反転入力端子に印加される前段の積分処理部16の出力電圧に対して所定の積分動作が行われる。

# [0059]

ところで、本実施形態のD/A変換器は、例えばテレビジョン受信機のRGB信号や輝度信号等の映像信号を得る回路として用いる用途に適している。具体的には、テレビジョン受信機用のD/A変換器は、図8に構成を示した回路をR、G、Bデータのそれぞれに対応させて3組備えており、1画面に対応するフレームを構成する各走査線毎に所定の時間間隔でそれぞれが8ビットのR、G、Bデータが入力されて、それぞれのデータを補間する連続的なR、G、Bアナログ電圧を生成する。

30

40

50

### [0060]

実際の積分回路では、出力電圧のドリフトが生じるため、この影響を取り除く回路を有することが好ましい。本実施形態では、前段の積分処理部16に含まれる演算増幅器141とキャパシタ143および抵抗145によって平均値を0レベルに保持する回路が構成されており、演算増幅器140等によって構成される積分回路の出力の平均値が常に0Vとなるように演算増幅器140の非反転入力端子の電圧レベルが調整される。

#### [0061]

後段の積分処理部18に含まれる演算増幅器152とキャパシタ153および抵抗155によって平均レベル保持回路が構成されており、演算増幅器150等によって構成される積分回路の出力の平均値が、演算増幅器151の非反転入力端子に印加される電圧レベルと同じになるように、演算増幅器150の非反転入力端子の電圧レベルが調整される。なお、演算増幅器151の非反転入力端子に印加される電圧レベルは、入力データそのものをアナログ電圧に変換してその平均レベルを求めたものが用いられ、この電圧レベルを求めるために、順次入力される入力データを保持するD型フリップフロップによって構成されるデータ保持部180と、この保持されたデジタルデータに対応するアナログ電圧を発生するD/A変換器182と、D/A変換器182の出力電圧を積分する積分回路184とが備わっている。

### [0062]

また、1フレーム毎に2つの積分処理部16、18に含まれる各積分回路の積分キャパシタに蓄積される電荷をリセットするために、スイッチ146、156が設けられており、垂直ブランキング信号がD型フリップフロップによって構成される同期化回路186によって同期化されて、垂直ブランキング期間に2つのスイッチ146、156がオン状態になる。このとき、演算増幅器140に接続されたキャパシタ142と演算増幅器150に接続されたキャパシタ152のそれぞれが放電され、それぞれの積分回路がリセットされる。

# [0063]

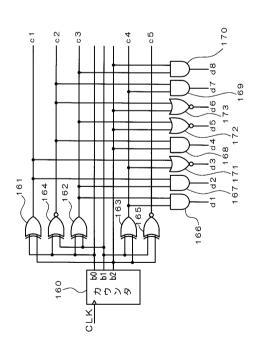

図11は、タイミング制御部20の詳細な構成を示す図である。同図に示すように、タイミング制御部20は、3ビットカウンタ160と、非反転出力を有する3つの排他的論理和回路161~163と、反転出力を有する2つの排他的論理和回路164、165と、非反転出力を有する3つの論理積回路166~170と、反転出力を有する3つの論理和回路171~173とを含んで構成されている。

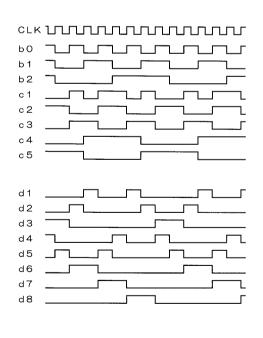

# [0064]

また、図12は、図11に示したタイミング制御部20の動作タイミングを示す図である。図12において示したCLK、b0~b2、c1~c5、d1~d8のそれぞれの波形は、図11においてそれぞれの符号を付した箇所に現れる波形を示している。図11および図12に示すように、3ビットカウンタ160は、入力されるクロック信号CLKに同期したカウント動作を行っており、このクロック信号が立ち上がる毎にカウントアップされ、3ビット出力b0、b1、b2が更新される。

# [0065]

上述したタイミング制御部20を用いて各階段関数発生部11-1~11-4に含まれる3つのスイッチのオンオフ状態を切り替えることにより、図7(C)、(E)、(G)、(I)に示した各階段関数を発生させることができる。具体的には、階段関数発生部11-1によって図7(C)に示した階段関数を発生させるために、この階段関数発生部11-1内の4つのトライステートバッファ100~106のオンオフ状態を、図11に示した論理和回路171の出力(d3)、論理積回路169の出力(d7)、論理積回路167の出力(d2)、論理積回路166の出力(d1)の論理状態によってそれぞれ切り替える。

# [0066]

同様に、階段関数発生部 1 1 - 2 によって図 7 (E)に示した階段関数を発生させるために、この階段関数発生部 1 1 - 2 内の 4 つのトライステートバッファ 1 0 0 ~ 1 0 6 のオ

ンオフ状態を、図11に示した論理和回路173の出力(d6)、論理積回路170の出力(d8)、論理和回路172の出力(d5)、論理積回路168の出力(d4)の論理状態によってそれぞれ切り替える。階段関数発生部11-3によって図7(G)に示した階段関数波形を発生させるために、この階段関数発生部11-3内の4つのトライステートバッファ100~106のオンオフ状態を、図11に示した論理積回路169の出力(d7)、論理和回路171の出力(d3)、論理積回路166の出力(d1)、論理積回路167の出力(d2)の論理状態によってそれぞれ切り替える。階段関数発生部11-4によって図7(I)に示した階段関数を発生させるために、この階段関数発生部11-4内の4つのトライステートバッファ100~106のオンオフ状態を、図11に示した論理積回路170の出力(d8)、論理和回路173の出力(d6)、論理積回路168の出力(d4)、論理和回路172の出力(d5)の論理状態によってそれぞれ切り替える。

### [0067]

なお、本発明は上記実施形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。例えば、上述した実施形態では、標本化関数を全域で1回だけ微分可能な有限台の関数としたが、微分可能回数を2回以上に設定してもよい。また、図1に示すように、本実施形態の標本化関数は、t=±2で0に収束するようにしたが、t=±3以上で0に収束するようにしてもよい。例えば、t=±3で0に収束するようにした場合には、図6に示したD/A変換器に含まれるデータ保持部や階段関数発生部のそれぞれの数を6とし、6個のデジタルデータを対象に補間処理を行ってこれらのデジタルデータをなめらかにつなぐアナログ電圧を発生すればよい。

#### [0068]

また、必ずしも有限台の標本化関数を用いて補間処理を行う場合に限らず、 - ~ + の 範囲で値を有する有限回微分可能な標本化関数を用い、有限の標本位置に対応する複数個 のデジタルデータのみを補間処理の対象とするようにしてもよい。例えば、このような標本化関数が二次の区分多項式で定義されているものとすると、各区分多項式を 2 回微分することにより所定の階段関数波形を得ることができるため、この階段関数波形を用いて電圧の合成を行った結果に対して 2 回の積分処理を行うことにより、デジタルデータに対応した電圧をなめらかにつなぐアナログ信号を得ることができる。

# [0069]

また、上述した実施形態では、 D / A 変換器の用途の一例としてテレビジョン受像器に使用する場合を説明したが、それ以外の用途、例えばコンパクトディスク等に記録されたデジタルのオーディオデータをアナログのオーディオ音声に変換する場合などに本発明の D / A 変換器を用いることができる。

# [0070]

# 【発明の効果】

上述したように、本発明によれば、順に入力される複数のデジタルデータのそれぞれに対応する所定の階段関数を発生させてこれらを加算し、その後この加算結果をアナログ電圧に変換して積分することにより連続的に変化するアナログ電圧が得られるため、最終的なアナログ信号を得るためにローパスフィルタを用いる必要がなく、扱う信号の周波数によって位相特性が異なるために群遅延特性が悪化するといったことがなく、歪みの少ない出力波形を得ることができる。また、オーバーサンプリングを行っていた従来の手法に比べると、部品の動作速度を上げる必要がないため、高価な部品を使用する必要がなく、部品コストの低減が可能になる。

### 【図面の簡単な説明】

【図1】本実施形態のD/A変換器における補間演算に用いられる標本化関数の説明図である。

- 【図2】標本値とその間の補間値との関係を示す図である。

- 【図3】図1に示す標本化関数を用いたデータ補間の説明図である。

- 【図4】図1に示した標本化関数を1回微分した波形を示す図である。

10

20

30

- 【図5】図4に示した折れ線関数をさらに微分した波形を示す図である。

- 【図6】本実施形態のD/A変換器の構成を示す図である。

- 【図7】本実施形態のD/A変換器の動作タイミングを示す図である。

- 【図8】図6に示したD/A変換器の詳細構成を示す図である。

- 【図9】階段関数発生部の詳細構成を示す図である。

- 【 図 1 0 】 変形後の階段関数と階段関数発生部内の各トライステートバッファのオンオフ 切替タイミングとの関係を示す図である。

- 【図11】タイミング制御部の詳細な構成を示す図である。

- 【図12】図11に示したタイミング制御部の動作タイミングを示す図である。

- 【図13】sinc関数の説明図である。

【符号の説明】

- 10-1、10-2、10-3、10-4 データ保持部

- 11-1、11-2、11-3、11-4 階段関数発生部

- 1 2 加算器

- 14 D/A(デジタル-アナログ)変換器

- 16、18 積分処理部

- 20 タイミング制御部

【図1】

【図2】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】 【図10】

【図11】 【図12】

【図13】

# フロントページの続き

(56)参考文献 米国特許第03543009(US,A)

KAMADA M ET AL, QUADRATIC SPLINE INTERPOLATOR, INTERNATIONAL JOUNAL OF SYSTEMS SCIENCE

,英国,1996年,vol.27,no.10,pages977-983

(58)調査した分野(Int.CI., DB名) H03M1/00-1/88